## Technology Mapping and Packing for Coarse-grained, Anti-fuse Based FPGAs

Chang Woo Kang, Ali Iranli, and Massoud Pedram

University of Southern California Department of Electrical Engineering Los Angeles CA, USA

- Introduction

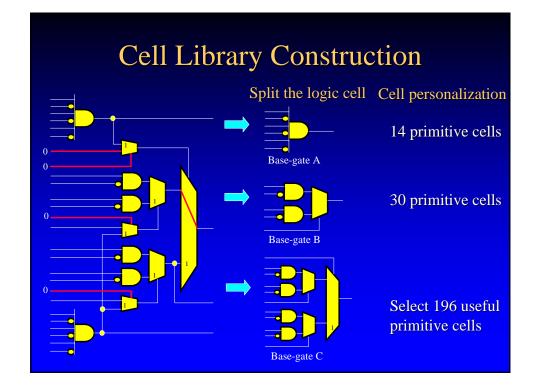

- Cell Library Construction

- Technology Mapping and Cell Packing

- Experimental Results

- Conclusion

## Introduction

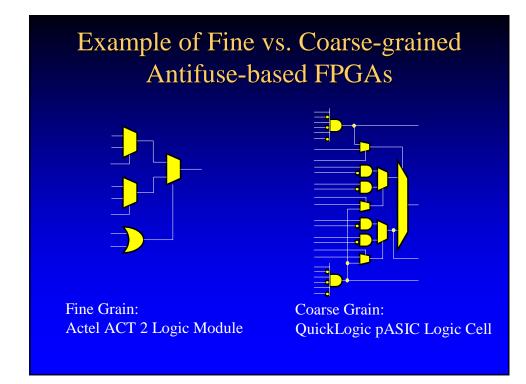

- Coarse-grained logic block architecture is widely used in the FPGA industry

- Xilinx Virtex series has 8 LUTs in a configurable logic block

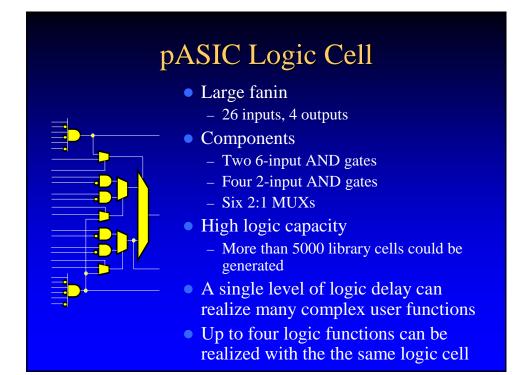

- QuickLogic pASIC series has 26 inputs in a logic cell

#### Cost Assignment for Primitive Cells

$$cell\_cost = \frac{s}{f \cdot c}$$

- Space usage, *s* : the amount of space in a pASIC cell that is used up by the primitive cell

- Freedom, *f* : the total number of places in a pASIC cell that the primitive cell can fit

- Coverage, *c*: complexity of the logic that the primitive cell can realize

- Notice that the inverter primitive cell does not have the minimum cost any more

#### The Coin-Change Problem

#### Problem statement

- Let  $c_1, c_2, ..., c_m$  be the coin types of a currency. Let  $C_i$  denote the value of coin  $c_i$  in cents and K be some integer. We assume  $C_1 = 1$ . The problem is to produce K cents of change by using a minimum number of coins

Minimize

$$\sum_{i=1}^{m} n_i$$

s.t.  $K = \sum_{i=1}^{m} n_i C_i$

where  $n_i$  denotes the number of coins of type i

Solution

$$count[K] = \begin{cases} 0 & \text{if } K = 0\\ \min_{i:C_i \le K} \{count[K - C_i] + 1\} & \text{if } K > 0 \end{cases}$$

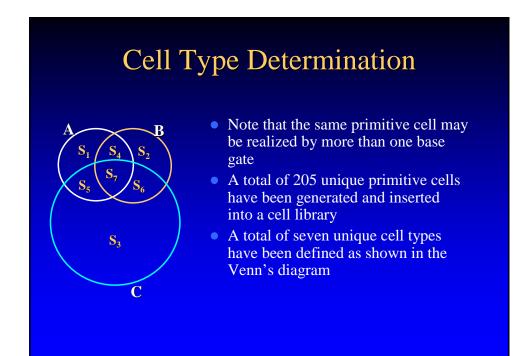

#### **Different Ways of Packing Cells**

|    | Combinations of<br>primitive cells |

|----|------------------------------------|

| 1  | $2S_5 + 2S_7$                      |

| 2  | $2S_4 + 2S_5$                      |

| 3  | $2S_5 + 2S_6$                      |

|    |                                    |

| i  | $\sum_{i=1}^{7} C_{i,S_j} S_j$     |

|    |                                    |

| 35 | $S_{3} + 2S_{7}$                   |

| 36 | $S_{3} + 2S_{4}$                   |

| 37 | $S_3 + S_4 + S_7$                  |

- 37 different cases of completely utilizing a logic cell

- *C<sub>i,Sj</sub>*: the number of primitive cells of type *S<sub>j</sub>* in the *i<sub>th</sub>* combination

- The packer must find optimal packing combinations in a bottom-up manner

#### **Exact Problem Statement**

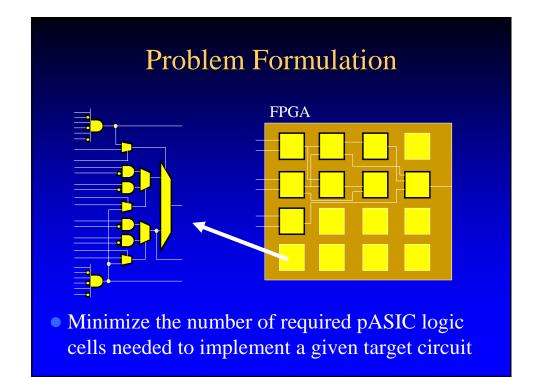

• Given the different ways of packing a pASIC3 logic cell as described in the previous table and a logic netlist generated by the min-cost technology mapper, find the minimum number of pASIC3 logic cells needed to cover all primitive cells in the logic netlist, i.e.:

Minimize

$$\sum_{i=1}^{37} n_i$$

s.t.  $\forall j : \sum_{i=1}^{37} n_i C_{i,S_j} \ge \left| S_j \right|$

where  $n_i$  denotes the number of packings of type *i* and  $|S_j|$  denotes the number of primitive cells of type *j* in the initial logic netlist

#### Analogy to the Coin-Change Problem

- After technology mapping, we count the number of primitive cells of each type,  $|S_1|,..., |S_7|$ . These are analogous to seven different target change counts

- The 37 different entries in the pASIC packing table are analogous to different currencies

- This is a multi-dimensional coin change problem, which can be solved optimally and efficiently by using a dynamic programming technique

# **Dynamic Programming Solution**

$$count(|S_{1}|,...,|S_{7}|) = \begin{cases} 0 & \text{if } \forall j, |S_{j}| \le 0 \\ \\ \min_{i:\forall j, C_{i,S_{j}} \le |S_{j}|} (count(|S_{1}| - C_{i,S_{1}},...,|S_{7}| - C_{i,S_{7}}) + 1) & \text{otherwise} \end{cases}$$

- Note that we must track remaining unpacked primitive cells for all seven cell types at the same time

- Computational complexity  $O(\prod_{i=1}^{7} |S_i|)$

|     | •     | , 1   |      | 1,    |

|-----|-------|-------|------|-------|

| HV1 | perim | antal | R DO | otte  |

|     |       |       |      | SUILS |

|     |       |       |      |       |

| Circuits | Primitive<br>cell count | 51 0                     |                            |                   | Dynamic programming based packing |                            |                   | Packing improvement             |                            |

|----------|-------------------------|--------------------------|----------------------------|-------------------|-----------------------------------|----------------------------|-------------------|---------------------------------|----------------------------|

|          |                         | Number of<br>logic cells | Cell<br>utilization<br>(%) | CPU time<br>(sec) | Number of<br>logic cells          | Cell<br>utilization<br>(%) | CPU time<br>(sec) | Number of<br>logic cells<br>(%) | Cell<br>utilization<br>(%) |

| Alu2     | 193                     | 76                       | 65.87                      | 0.08              | 51                                | 100                        | 50.27             | 32.9                            | 34.1                       |

| Alu4     | 377                     | 150                      | 65.11                      | 0.34              | 101                               | 98.43                      | 960.59            | 32.7                            | 33.9                       |

| Арехб    | 349                     | 154                      | 59.86                      | 0.37              | 117                               | 80.23                      | 306.24            | 24                              | 25.4                       |

| Dalu     | 471                     | 194                      | 63.39                      | 0.56              | 138                               | 90.75                      | 143.81            | 28.9                            | 30.1                       |

| C1355    | 210                     | 83                       | 64.81                      | 0.11              | 58                                | 93.75                      | 1.37              | 30.1                            | 30.9                       |

| C1908    | 213                     | 96                       | 58.84                      | 0.13              | 74                                | 77.74                      | 20.54             | 22.9                            | 24.3                       |

| C432     | 108                     | 45                       | 65.85                      | 0.03              | 31                                | 100                        | 13.36             | 31.1                            | 34.2                       |

| C499     | 210                     | 83                       | 64.81                      | 0.11              | 58                                | 93.75                      | 1.37              | 30.1                            | 30.9                       |

| C3540*   | 657                     | 268                      | 64.22                      | 1.2               | 191                               | 91.89                      | 56.21             | 28.7                            | 30.1                       |

| C880     | 214                     | 92                       | 62.76                      | 0.12              | 64                                | 93.45                      | 45.95             | 30.4                            | 32.8                       |

| C5315*   | 764                     | 333                      | 59.97                      | 1.94              | 256                               | 79.09                      | 42.97             | 23.1                            | 24.2                       |

| C6288*   | 1457                    | 664                      | 55.19                      | 13.11             | 593                               | 61.84                      | 19.14             | 10.7                            | 10.8                       |

| C7552*   | 1052                    | 413                      | 64.94                      | 3.7               | 312                               | 86.51                      | 86.06             | 24.5                            | 24.9                       |

| Average  |                         |                          |                            |                   |                                   |                            |                   | 26.9                            | 28.2                       |

\*The packing algorithm used segmented lists so as not to exceed the amount of available memory in the computer

# Conclusions

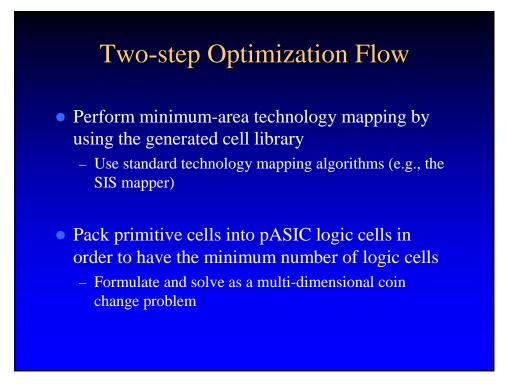

- Proposed a minimum-area packing algorithm for coarse-grained, anti-fuse based FPGAs, comprising of library generation, technology mapping and cell packing.

- Solution of a multi-dimensional coin-change problem resulted in a polynomial time optimal solution to the cell packing problem

- Our algorithm resulted in an average of 27% fewer logic cells compared to a greedy algorithm