## Library Design

- Low power versus high performance

- Static versus dynamic

- CMOS complementary versus pseudo-NMOS

- Library-based versus on-the-fly-synthesized

- · Characterization and modeling issues

## Putting It Together

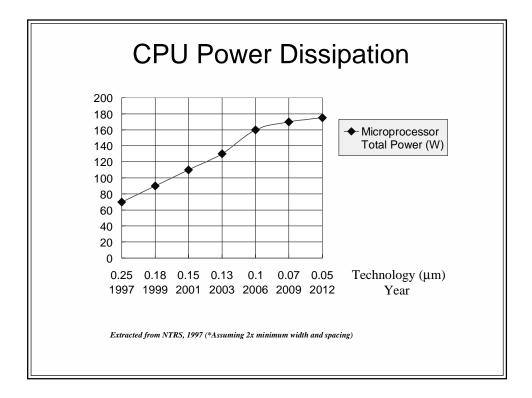

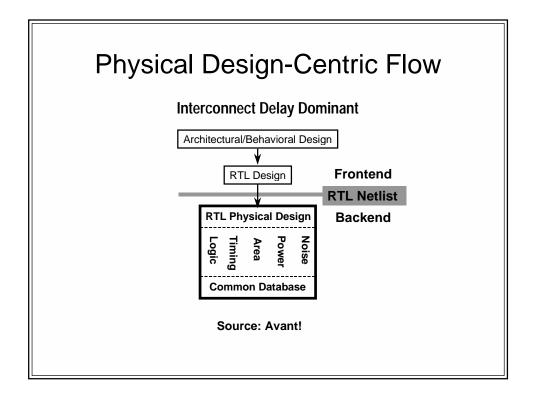

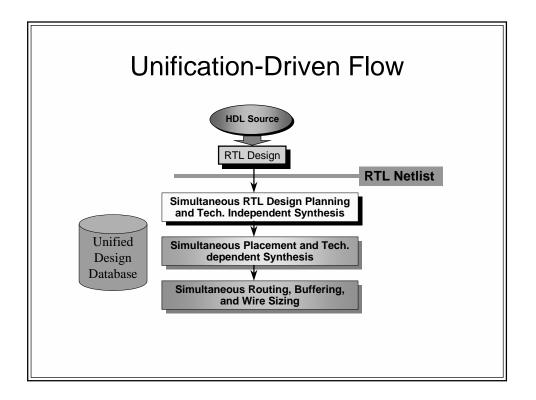

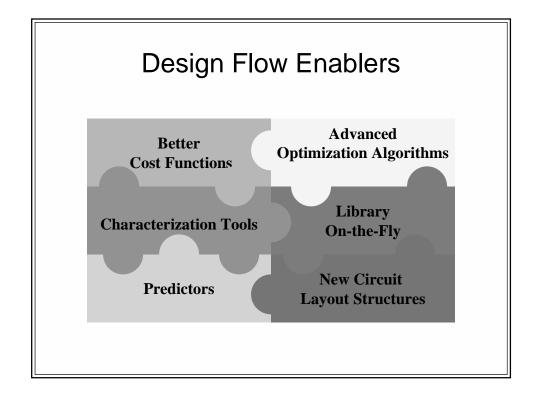

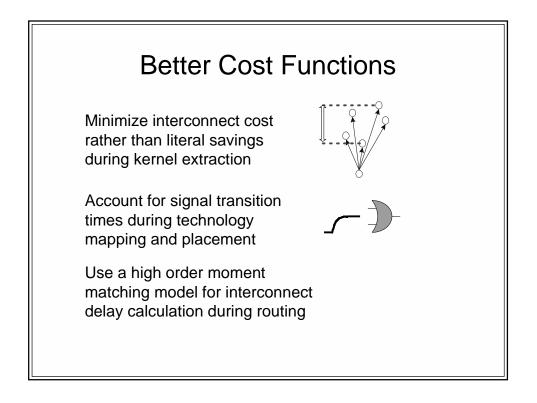

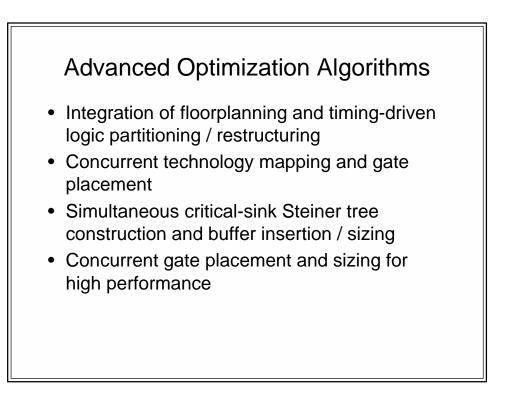

- Front-end optimization tools must be able to cope with the increasing complexity of DSM circuits

- Back-end analysis tools should handle complicated second-order effects in DSM circuits

- Must have

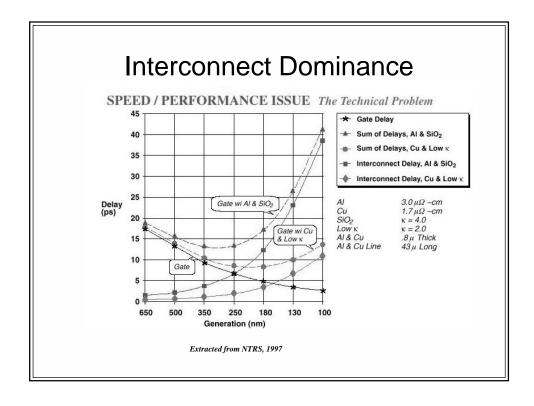

- interconnect-optimized process technologies

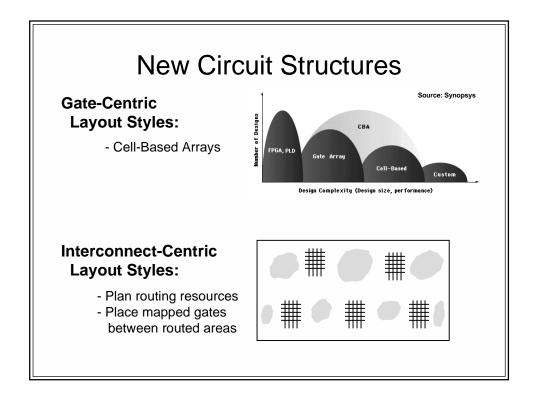

- new circuit layout structures

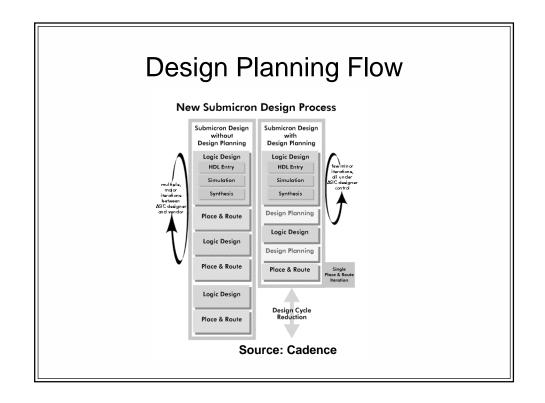

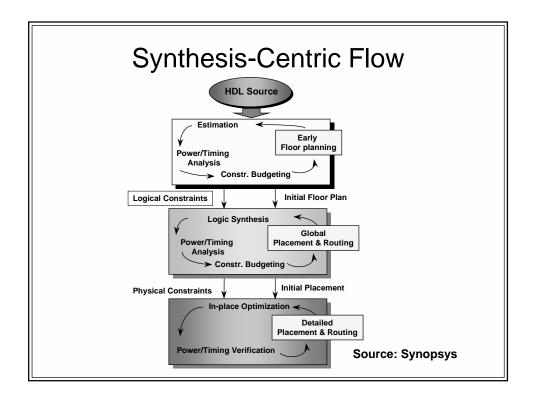

- interconnect-driven design flows, algorithms and tools

- signal integrity modeling and characterization tools

- ability to handle multiple constraints at all levels of abstraction

- industry standards

|        | Conventional |     |       | SiMPA-E  |           |         | Area Ratio Delay Ratio |            |            |             |

|--------|--------------|-----|-------|----------|-----------|---------|------------------------|------------|------------|-------------|

|        | Gate Area    |     |       |          | Gate Area | -       | 1                      | Total Area | Area Natio |             |

| tree6  | 7260         | 3   |       | 10428    | 7260      |         | 1.82                   |            | 89.87%     | 106.43%     |

| tree8  | 10054        | 3   | 0.89  | 14441    | 10347     | 2       |                        |            | 92.49%     |             |

| tree16 | 17732        | 4   | 1.08  | 28049    | 18002     |         | 1.23                   |            |            |             |

| tree20 | 30536        | 5   |       | 52744    | 31224     |         | 1.62                   |            |            |             |

| tree32 | 38665        | 6   | 1.81  | 72409    | 39149     |         |                        | -          | 85.52%     | 103.87%     |

| tree48 | 66396        | 7   | 2.58  | 133999   | 68432     | 4       | 2.38                   | 108247     | 80.78%     | 92.25%      |

|        |              |     |       |          |           |         |                        |            | 86.09%     | 101.99%     |

|        | Conver       |     |       | entional |           | SiMPA-D |                        |            | Area Ratio | Delay Ratio |

|        | Gate Area    | Cut | Delay |          | Gate Area |         |                        |            |            |             |

| tree6  | 9482         | 3   |       |          | 10103     |         |                        | 13042      | 95.76%     | 78.71%      |

| tree8  | 13444        | 4   | 0.75  | 21266    | 15154     | 3       | 0.61                   | 21767      | 102.35%    | 81.33%      |

| tree16 | 22304        | 5   | 0.98  | 38525    | 19098     | 4       | 0.65                   | 30210      | 78.42%     | 66.33%      |

| tree20 | 51030        | 6   | 1.03  | 95565    | 54342     | 5       | 0.78                   | 93863      | 98.22%     | 75.73%      |

| tree32 | 48468        | 6   | 1.27  | 90767    | 50015     | 5       | 0.89                   | 86390      | 95.18%     | 70.08%      |

| tree48 | 90342        | 7   | 1.92  | 182327   | 85796     | 6       | 1.47                   | 160673     | 88.12%     | 76.56%      |

|        |              |     |       |          |           |         |                        |            | 93.01%     | 74.79%      |

## Conclusion

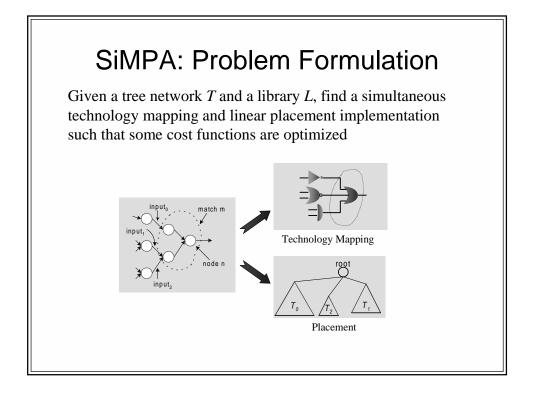

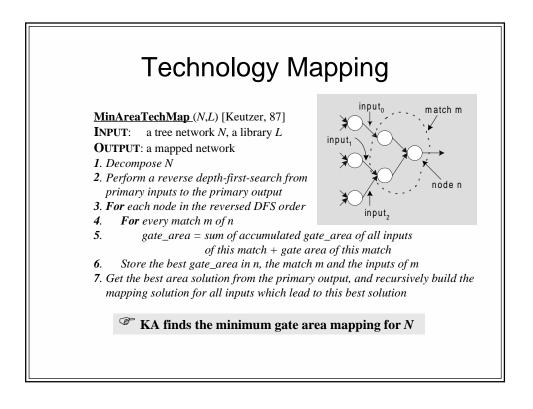

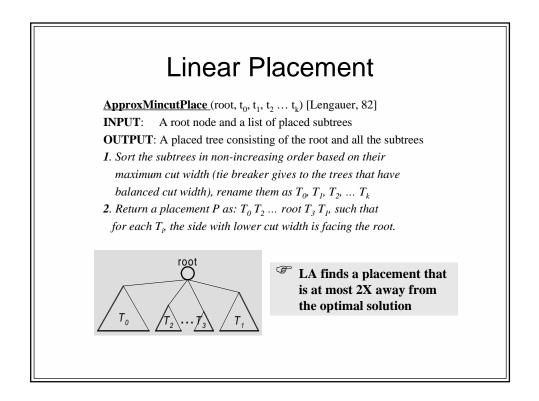

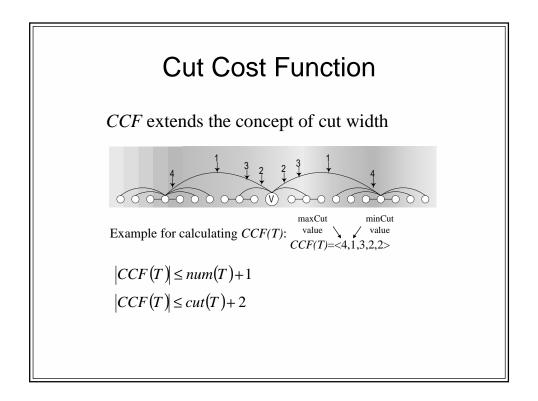

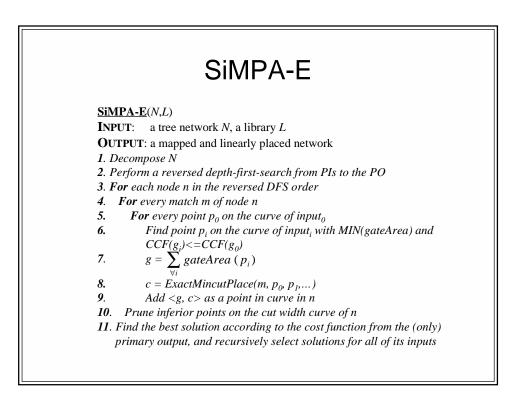

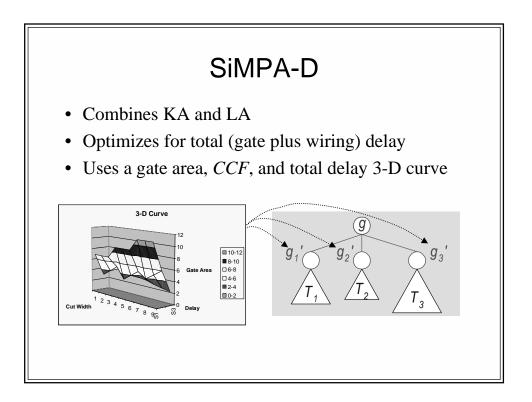

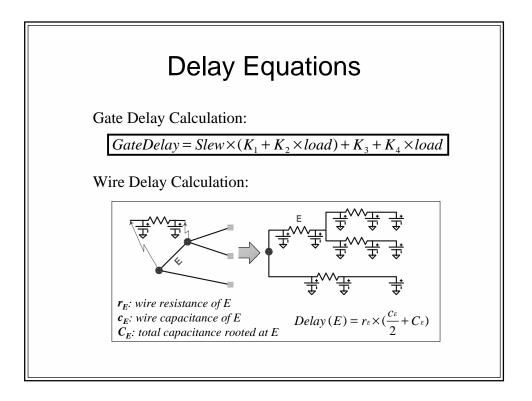

- SiMPA optimally solves the simultaneous technology mapping and linear placement problem for tree-structured circuits

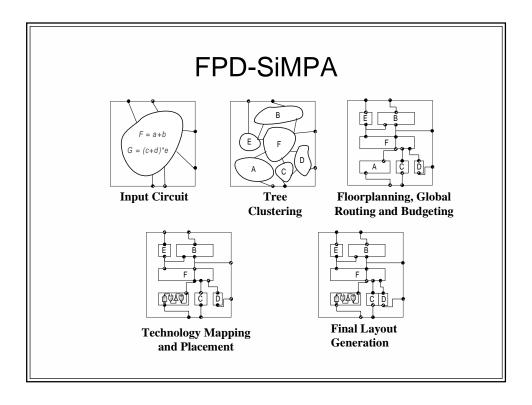

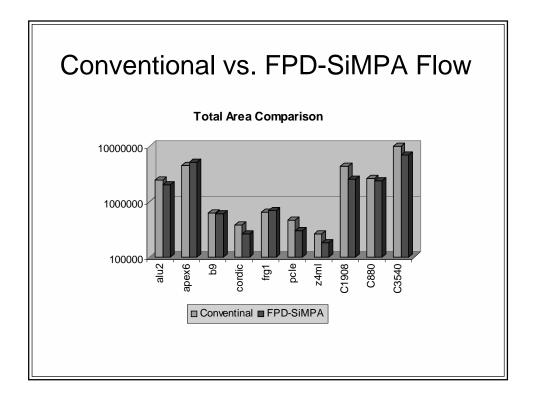

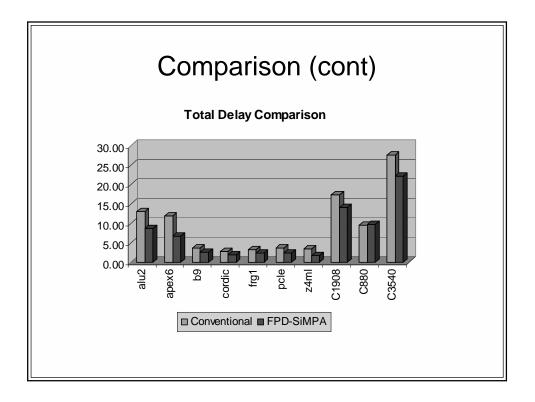

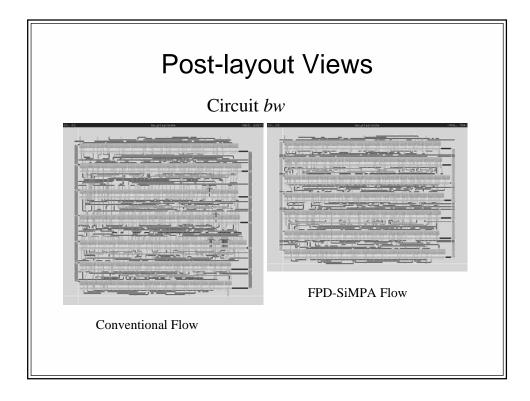

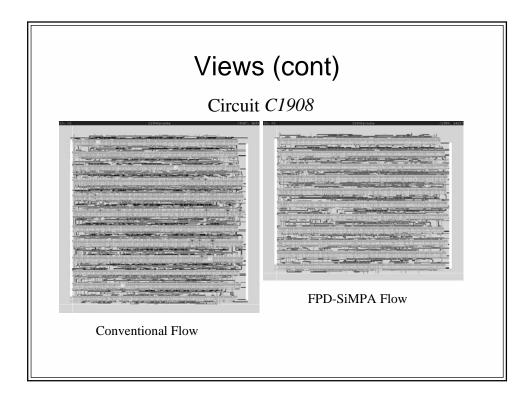

- FPD-SiMPA combines floorplan-driven flow and SiMPA to produce high quality solutions for general circuits

- Future work will focus on developing non-tree circuit partitioning, direct two-D placement, and global wire planning.