## Runtime Mechanisms for Leakage Current Reduction in CMOS VLSI Circuits

Afshin Abdollahi University of Southern California

Farzan Fallah Fujitsu Laboratories of America Massoud Pedram University of Southern California

## Conclusions

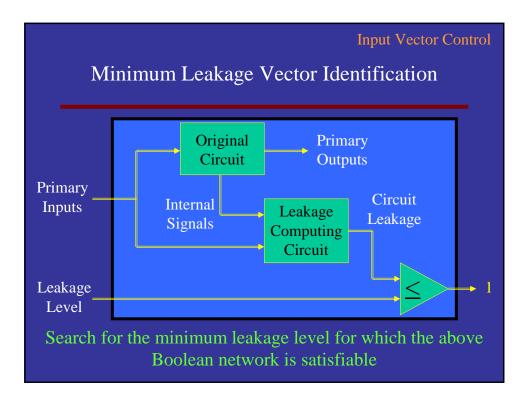

- Two runtime mechanisms for reducing the leakage current of a CMOS circuit are presented

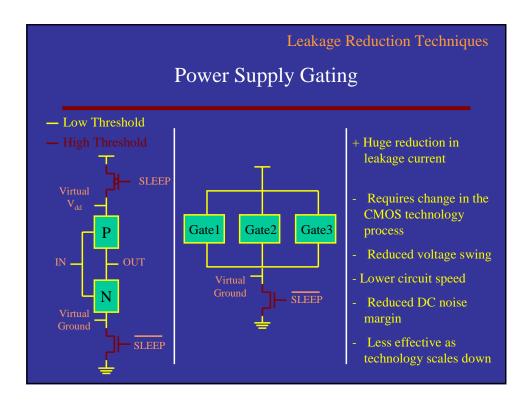

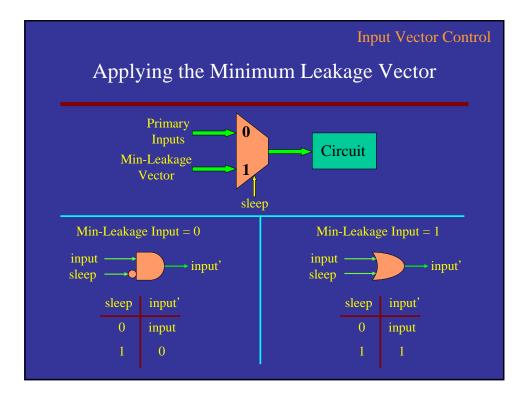

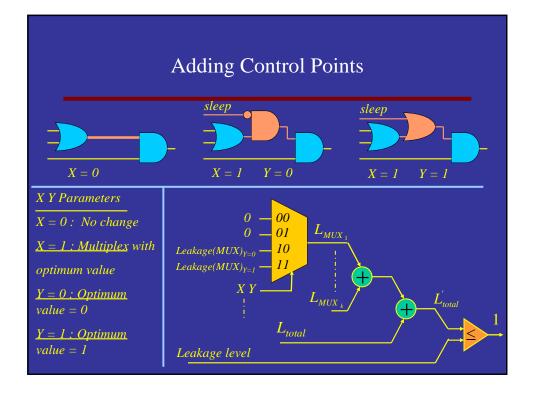

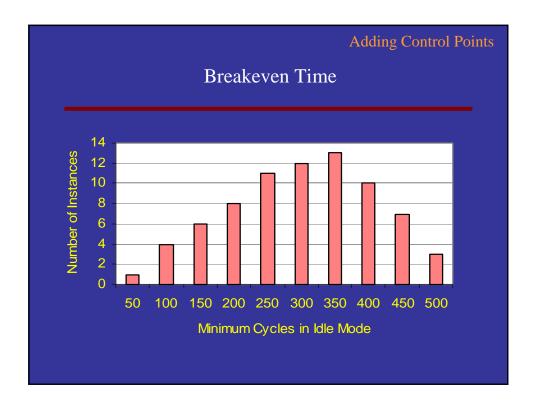

- A "sleep" signal is used to shift in a new set of external inputs and pre-selected internal signals into the circuit so as to minimize the total leakage current in the circuit

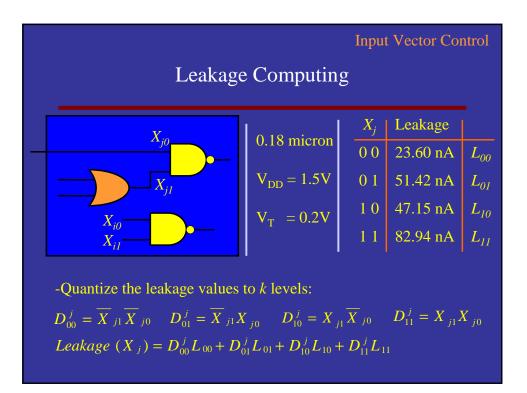

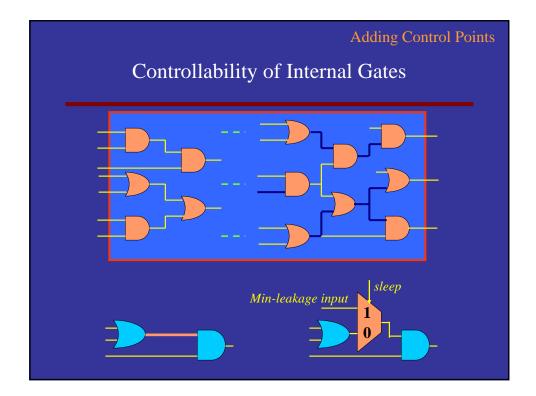

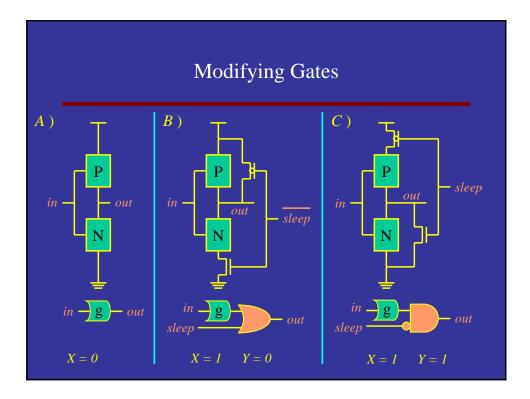

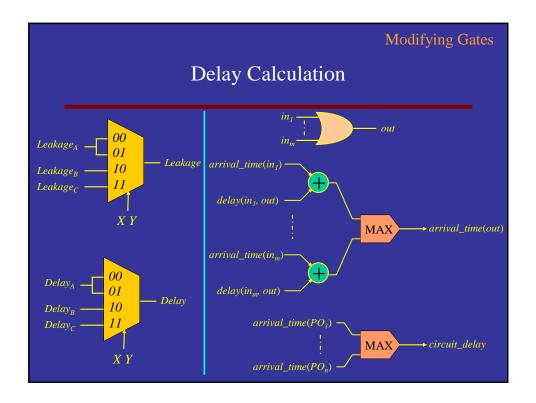

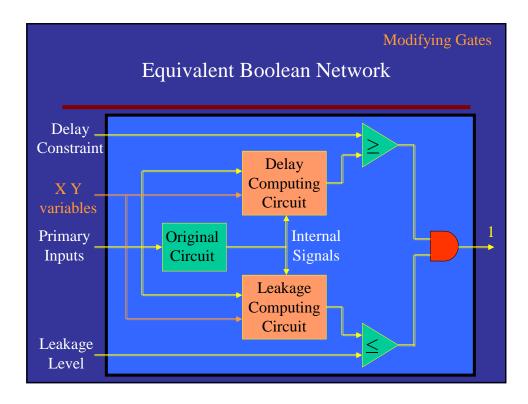

- NMOS and PMOS transistors are added to some of the gates in the circuit to increase the controllability of the internal signals of the circuit and decrease the leakage current of the gates using the "stack effect"

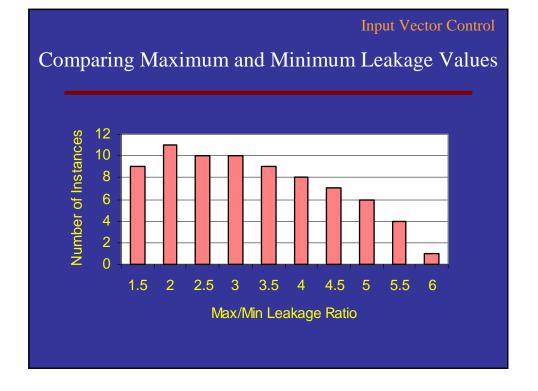

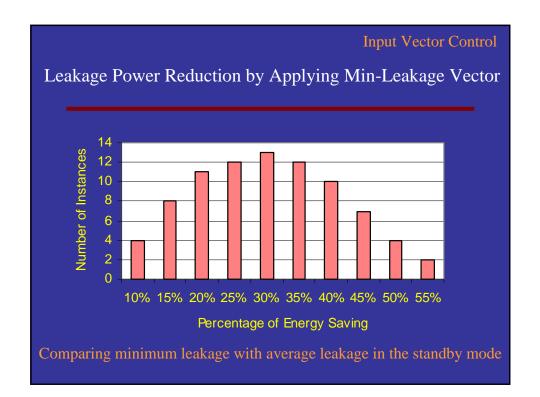

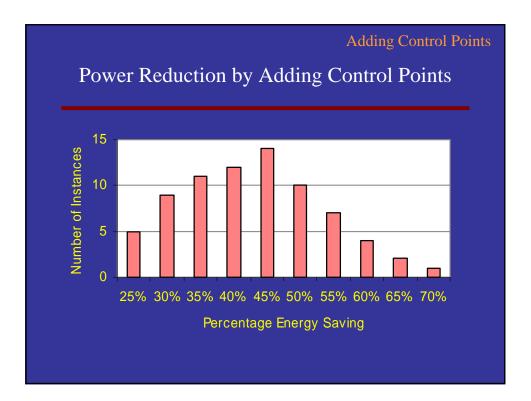

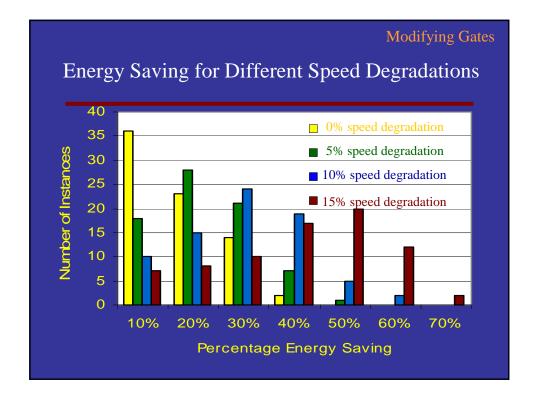

- Experimental results on the circuits in the MCNC91 benchmark suite demonstrate that it is possible to reduce the leakage current by up to 70% in VLSI circuits at the expense of a very small overhead.