# Effects of Placement and Gate Sizing

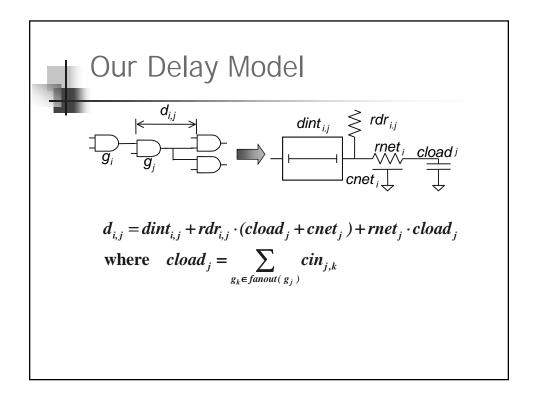

### Placement

- Assign the cells to suitable locations

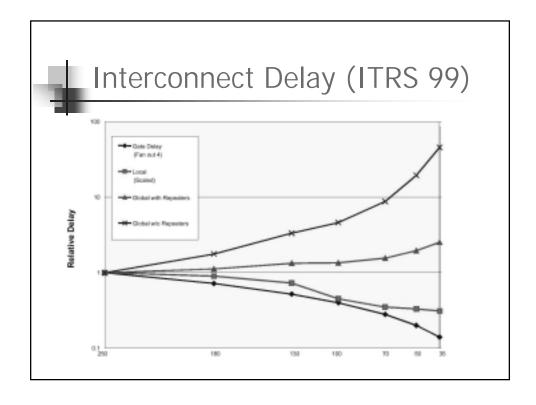

- Optimize the interconnect delay

- A poorly placed layout cannot be improved by a subsequent high quality routing

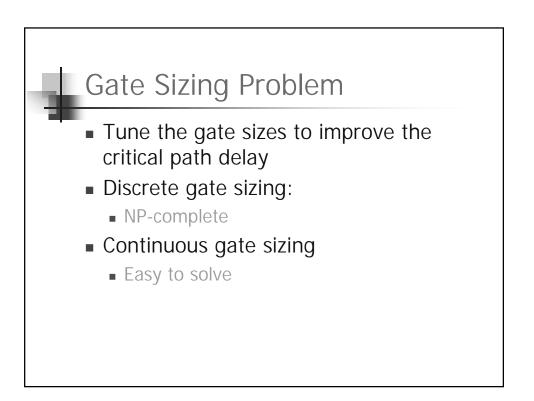

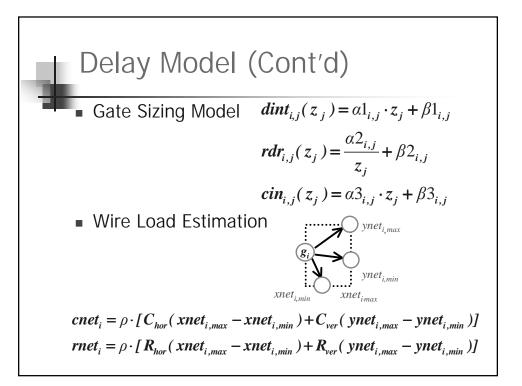

### Gate Sizing

- Tune the size of each cell

- Optimize the gate delay

- Balance the path delays in the circuit

## Placement Problem

- Given a collection of cells with ports on the boundaries, the dimensions of these cells, and a collection of nets, the process of placement consists of finding suitable physical locations for each cell

- NP-complete

- Traditional objective minimize wire length

- More recent objective improve performance

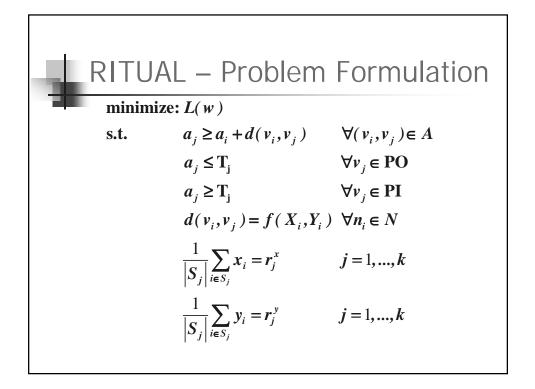

Lagrangian Relaxation

minimize

$$\frac{1}{2}w^TQw + b^Tw$$

s.t.  $Aw \le c$

$\max_{\lambda \ge 0} (\min_x (\frac{1}{2}w^TQw + b^Tw + \lambda^T(Aw - c)))$

$w^{(k+1)} = -Q^{-1}[\lambda^{(k)}A + b]$

## RITUAL – Reducing The Problem Size

- The above problem formulation becomes too large if we include all the cells in the circuit

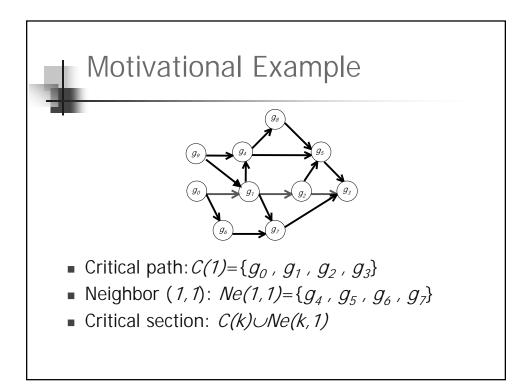

- Reduced active forest (RAF): the set of paths connecting to the POs that violate timing requirements

- The problem formulation only contains timing constraints for RAF

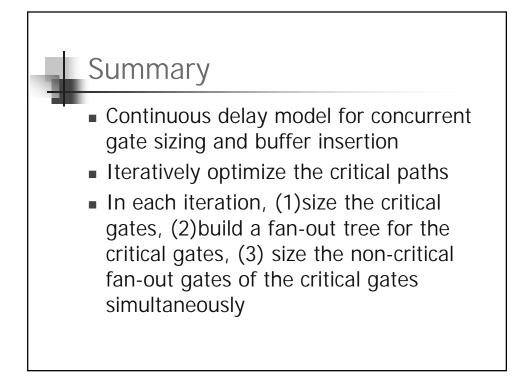

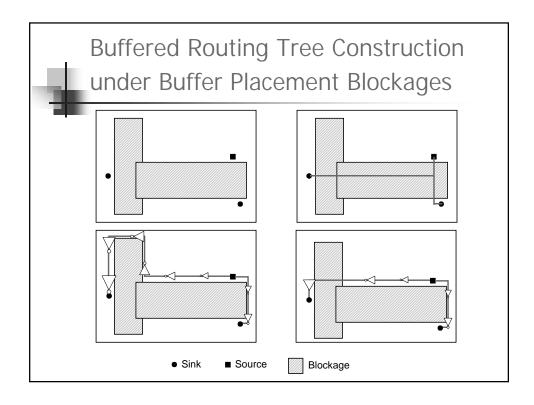

# Problem Definition

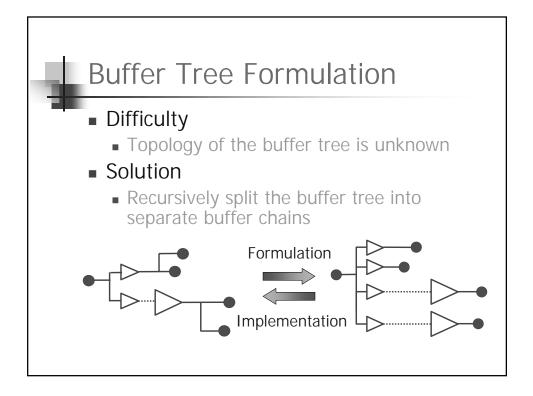

Given (1) a set of placement blockages, where routing is allowed but no buffers can be placed and (2) the locations of the source and the pins of a net, simultaneously build the net topology and insert sized buffers/inverters at the places where they are permitted to improve the timing of the net